# 絕緣層上覆矽結構矽鍺異質接面電晶體的埋氧化層厚度對元 件之影響

廖淑慧 林聖凱 黃喬聯 李麗英 中州技術學院電子工程系 51003 彰化縣員林鎮山腳路三段二巷六號

## 摘要

本論文利用 TCAD 半導體元件模擬器探討埋氧化層在絕緣層上覆矽異質接面雙極性電晶體中的影響因素。論文中詳細使用模擬器分析元件的物理與電學特性,例如Early 電壓、截止頻率,以及最大共振頻率。本研究並比較具有埋氧化層的元件和傳統塊材元件的最大共振頻率,發現具有埋氧化層的元件優於傳統塊材元件結構。我們也發現最大共振頻率有隨著埋氧化層厚度遞增的趨勢。

關鍵詞:矽鍺,異質接面電晶體,Early 電壓,截止頻率,最大共振頻率

# Study of Oxide Thickness Effect on the Performance of SiGe HBTs with SOI Structure

SHU-HUI LIAO, SHENG-KAI LIN, QIAO-LIAN HUANG, AND LI-YING LEE

Department of Electronic Engineering, Chung Chou University of Science and Technology,

Changhua County 51003, Taiwan

#### **ABSTRACT**

Using a TCAD simulator, the oxide thickness effect on electrical characteristics of the SiGe HBT on SOI substrates were examined. This effect on Early voltage, cut-off frequency, and maximum oscillation frequency for SiGe HBT on SOI substrate were investigated. It is found that the maximum oscillation frequency ( $f_{max}$ ) of SiGe HBT on SOI substrate is much better than that of conventional SiGe HBT. The maximum oscillation frequency increases with the increase in oxide thickness and tend to saturate at oxide thickness of 0.15  $\mu$  m.

Key Words: TCAD, SiGe, HBTs, self-heating effect.

#### 一、前言

近年來矽基元件已成爲研究的主流之一[1-5]。雙極性電晶體在通信系統中扮演著重要的角色,例如高速數位通信、類比/混合信號應用等。由於矽基元件具有低價、高可靠性以及積體化的特性,在某些領域之應用可與三五族元件互相抗衡。由於矽鍺異質結構電晶體的基極能隙較小,所以在順向偏壓時與傳統的同質結構相較之下,具有較大的集極電流。此外,漸變式的能隙變化,使得少數載子在穿越基極時能夠以較快之速度通過[6]。根據研究顯示,在基極加入較多的鍺元素時,可以加強長波長波段的吸收效果[7],然而,鍺元素的加入卻也使得元件的基極產生對應的應變效果。所以鍺元素在基極的濃度變化特性曲線與含量在矽鍺異質結構電晶體元件的功能展現上,扮演極重要的角色。接著,分析矽鍺異質結構電晶體在絕緣層上長晶的特件。

矽鍺異質結構雙極性互補金屬氧化物半導體 (SiGe-BiCMOS) 製程由於元件產品的優越性能特色,已 成爲各種電子產品的製程主流。由於雙極性互補金屬氧化物 半導體技術一方面需要 CMOS 提供數位功能之呈現再加上 須以雙極性電晶體提供 RF 與類比功能的需求,目前矽鍺異 質結構雙極性互補金屬氧化物半導體製程已廣泛的使用絕 緣層上覆矽(SOI, silicon-on insulator)技術。 SOI 技術是 由 IBM 研發成功,主要是在矽晶片下添加氧化物的絕緣 層,避免電氣效應,以降低電源消耗,減少電流的流失,加 快 IC 的處理速度。SOI 技術除了可應用在需要較低電源消 耗的設備上,如行動電話、手錶等,爲了能充分發揮 SOI 高速作業的特點,目前亦積極朝高頻率 IC 應用發 展。關於絕緣層上覆矽之矽鍺異質結構雙極性電晶體(SiGe HBT on SOI substrate)的元件特性,有許多的研究單位針對 集極完全空乏(fully depleted collector)的狀況下元件的功能 評估。透過這些實驗或理論模擬研究顯示此種結構之元件在 集極完全空乏時,可以提供較高之崩潰電壓 (BV<sub>CEO</sub>, base-collector breakdown voltage )、較大之 Early 電壓 (V<sub>A</sub>, Early voltage),以及較佳之崩潰電壓-截止頻率  $(BV_{CEO} ext{-}f_T)$  之取捨。在本論文中,我們使用極適合用以探 討半導體元件特性評估之元件模擬器 DESSIS-ISE 作爲主要 的研究工具。我們首先探討矽鍺異質結構電晶體積極摻雜鍺 元素的特性。最後,我們分析了矽鍺異質結構電晶體在絕緣 層上長晶的特性。透過二維模擬演算,我們展示了當絕緣層

上覆矽之矽鍺異質結構雙極性電晶體使用特定厚度的氧化 層時,元件的直流電學特性。

使用絕緣層上覆矽技術的主要缺點之一,是伴隨絕緣層所產生的嚴重熱效應(thermal effect),氧化層的添增雖然提升了元件的性能卻也同時阻礙了熱的傳導,因而促使元件出現熱的不穩定(thermal instability)現象與問題[15-19]。此種元件的自我加熱效應(self-heating effect)不僅降低元件的性能,亦嚴重影響元件在長時間使用情況下的可靠度(long-term reliability)。爲能精確建立元件使用絕緣層上覆矽技術的模型,不論是元件的最佳化設計或是配合相關的電路設計,溫度效應的考量是必須的。所以,我們也仔細的分析了元件的熱阻(thermal resistance)。

# 二、外質半導體之載子濃度

#### 2-1 p-n 接面的能帶圖

當純的半導體材料被摻雜(Doping)雜質後,半導體變成為外質性(Extrinsic),這些雜質爲週期表的第三與第五族元素,摻雜的結果產生二個外質半導體,由增加的載子型態分別,有 n 型和 p 型半導體。要產生一個 n 型半導體,典型的第五族摻雜元素爲磷(P)、砷(As)及銻(Sb),在它們的最外圍具有 5 個電子稱爲施體(Donor)雜質,此時共價鏈上會多出一個電子,這個電子變成自由電子而只受原子間格影響。矽原子得的中心被五價的磷原子所取代 4 個磷原子的共價電子和圍繞矽原子的 4 個電子形成共價鏈結,第 5 個所謂"額外"的電子只是疏鬆於磷原子核,在能帶圖中,這個電子所佔據能態是在能隙內,即位於傳導底下,其間隔爲  $E_d$ 的地方,因  $E_d << E_g$ ,所以從這個能階把電子激發傳導代所需的能量。n 型半導體中,這個數目較多的載子即傳導帶中的電子,稱爲該半導體的多數載子(Majority),數目較少的載子即價帶中的電洞,是爲少數載子。

一個半導體材料被稱為 p 型式當一個三族加入純半導體中,一般的摻雜雜子爲硼(B)、鎵(Ga)與銦(In),這些摻雜的原子具有三個位圍電子,而當取代在晶格中的半導體原子,因此,摻雜原子可以接受一個電子,這個型態的電子稱爲受體(Acceptor)雜質,一個額外的電子便被"接受"在硼原子四週而行成四個共價鏈,而一帶正的"電洞"便產生在價代帶上,這個是所謂 p 型半導體。p 型半導體是四價的矽原子其中之一被三價的硼原子所取代,硼原子只可何和三個矽電子共價鏈結,所以在此過程中,硼一矽鏈結產生一個電洞。

只需要一很小的能量,電子便可從鄰近的矽一矽鏈結中扯離 而去填滿電洞,使得價帶上留下一個電洞,以相似方式,電 子可以從其它鏈結中移入第二個電洞,因此電洞可在晶格遷 移。

#### 2-2 異質接面雙載子接面電晶體

一般所謂電晶體是指雙載子接面電晶體,同時電晶 體的原文乃代表轉移電阻,是一個多重接面(兩個接面)之半 導體元件,換言之,意指一個可以將輸入電流訊號加以放大 成爲電壓訊號之轉移電阻放大器,通常電晶體會與他電路元 件整合在一起,已獲得電壓、電流,或是信號之功率增益。 所謂異質接面雙載子電晶體(HBT)是指電晶體中之一或二 接面是由不同能隙之半導體材料所構成,而得到較佳的操作 特性。HBT 主要的優點是射極注入效率(γ)較高,其基本之 操作原理和同質材料之雙載子電晶體相同,但在高速度和高 頻率之操作上深具潛力,因爲這些特質,HBT 在光電微波 和數位應用設計上非常受到歡迎。關於同質結構與異質結構 接面電晶體能帶關係之比較,同質結構之接面電晶體其中  $qV_n = qV_p$ ,而一直接面電晶體則爲  $qV_n < qV_p$ ,以製程技術 言,同質接面雙載子並無能隙差之存在,故必須將射極和基 極的摻雜濃度比提到非常高,反之異質結面電晶體則不需要 ,正如前面所談及  $qV_n < qV_p$ ,與同質接面作比較,由 n 型射 極注入電子到基極所要克服的位能障  $qV_n$  比電洞由基極注 入射極所要克服位能障 qV, 爲低, 換言之, 在同樣摻雜濃度 下之射極條件下,射極注入電子至基極之位能障之位能障比 先前用同質結構之位能障低了很多,如此因而提高射極電子 之注入效率,導致增進異質接面電晶體電流之放大率,同理 射極就不需要一定要使用重掺雜之製程技術,這個優越特性 正是電晶體操作工作時最想要的部份。

#### 2-3 能帶工程(Bandgap Engineering)

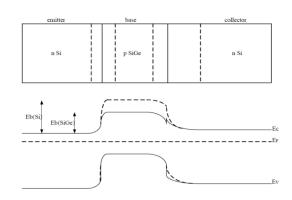

矽鍺異質接面電晶體像三明治一樣,基極的矽鍺被集極和射極的矽夾在中間,我們可由能帶的比較來了解矽鍺異質接面電晶體與同質介面矽電晶體有何不同。由圖 2-1 之能帶圖可知,在價帶上(valence band),基射極/基集極的異質接面處可看出能帶不連續,而在傳導帶(conduction band)上則有一個突起(spike)的情形。傳導帶上關係到電子由射極流向基極的電位障(conduction band barrier)E<sub>b</sub>,可明顯看出矽鍺電晶體中的 E<sub>b</sub> 比矽電晶體還小,意味著矽鍺電晶體中

基極的電子將更容易越過電位障到達射極,同樣的,在給定相同的基射極電壓時,異質接面電晶體將比矽電晶體獲得更多的集極電流;同樣的影響電洞的電位障發生在價帶上,但是在這部份矽與矽鍺並無太大差異,故在這兩種元件中的基極電流可視爲相同。

圖 2-1 矽鍺異質接面電晶體(實線)與雙載子矽電晶體(虛線)能帶圖的比較。實線部分是矽鍺異質接面電晶體, 虛線部分爲雙載子係電晶體當加入鍺時能帳就會下降,所已在基極區加入 Ge 可以提升加入電子的能障。

### 三、結果與討論

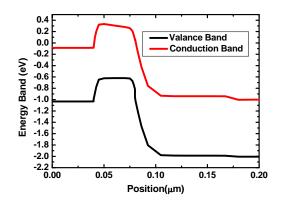

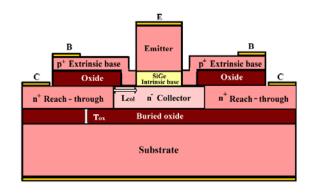

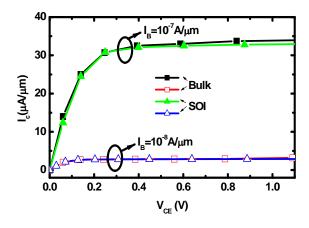

在本論文中,我們探討矽鍺異質結構電晶體的元件特性。圖 3-1.是元件的能帶圖。電晶體的偏壓條件是  $V_B$ =0.6V and  $V_C$ =1V。模擬結果顯示,能帶圖由於基極區加入漸變層的矽鍺合金,鍺的濃度由射、基極接面處的最小值(0%)增加至基、集極接面處的最大值(13%),使得能帶圖改變,形成在基、集極接處下拉的效應。最後我們在元件的設計上使用了「絕緣層上覆矽」(SOI)的結構(圖 3-2),並用二維的元件模擬分析,比較絕緣層上覆矽與傳統塊材結構(bulk structure)的直流輸出特性曲線。模擬結果顯示 SOI 的結構有較好的輸出特性。

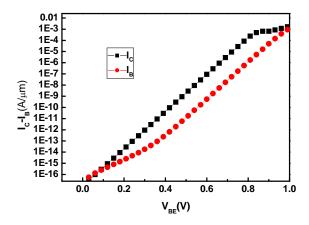

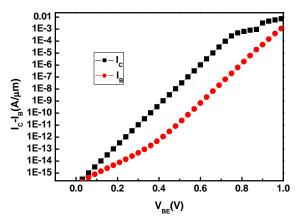

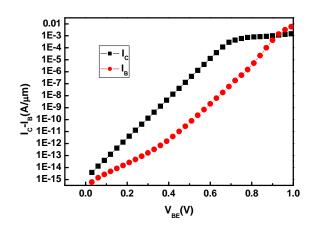

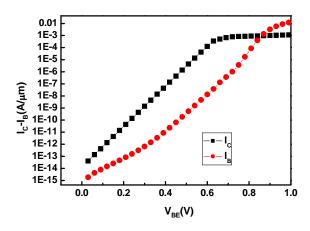

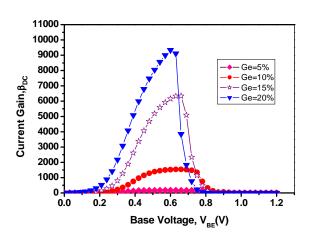

由於在基極區 Ge 摻雜濃度扮演重要的腳色,所以我們針對不同的 Ge 摻雜濃度的莫耳分率做分析。圖  $3-4 \times 3-5 \times 3-6$ ,以及 3-7 分別是針對不同的 Ge 莫耳分率的情況下  $I_C$  和  $I_B$  對  $V_{BE}$  的特性曲線圖。圖 3-8 則是針對結果所對應的直流電流增益。模擬結果顯示 Ge 的濃度愈高,增益愈顯著。元件在工作中會產生自我加熱效應(self-heating effect)的問題在所有的 SOI 技術中是一個眾所皆知的缺點。傳統使用的塊材式矽鍺異質結構雙極性電晶體,元件產生的熱可以

快速的分散於次集極並且通過矽基板,完成熱的排出。若使用了 SOI 的結構,氧化層的存在適足以有效的阻斷既有的傳熱路徑,實乃因氧化層具有較小的熱傳導(thermal conductivity)之故。當電晶體在工作時,元件內部會產生功率耗散(power dissipation),導致接面溫度(junction temperature)與環境溫度(ambient temperature)的差異,熱電阻(thermal resistance)可用以測量接面溫度與環境溫度之間的差異[15-19],其關係爲

$$T_{iunction} = T_{ambient} + R_{th} \times P_{diss}$$

(1)

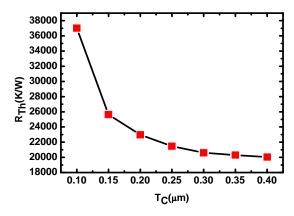

其中  $R_{th}$  是熱電阻, $P_{diss}$  是電晶體內部的功率耗散。 在使用元件模擬器進行溫度效應的模擬過程,爲了粹取熱電阻,我們在元件中自行生產一個提供 1 mW 的功率產生器 (reference power)以作爲模擬元件本身自我加熱效應。利用 ISE-TCAD 的 Dessis 可以由給定的功率計算出溫度在元件中的分布。首先將 B-C 接面或其他特定區域的溫度讀取並取平均值算出所需的接面溫度,再代入方程式(1),即可獲得對應的熱電阻。我們探討了絕緣層上覆矽之矽鍺異質結構雙極性電晶體元件本身自我加熱效應隨著不同的集極厚度  $T_{C}$  之厚度的變化,並將對應的熱電阻特性曲線圖繪製於圖 3-9。分析結果顯示熱電阻隨著集極厚度  $T_{C}$  的增加而下降。如同前文所述,氧化層的加入勢必造成阻礙散熱的相當影響、增加熱電阻。然而我們發現熱電阻是可以經由增加集極厚度來獲得舒緩。這樣的模擬結果,讓我們在使用 SOI 結構時可以配合集極厚度的適當選擇,來改善熱效應。

#### 四、結論

在本論文中,我們探討矽鍺異質結構電晶體的元件特性。用二維的元件模擬分析,比較絕緣層上覆矽與傳統塊材結構(bulk structure)的直流輸出特性曲線。模擬結果顯示 SOI的結構有較好的輸出特性。

由於在基極區 Ge 摻雜濃度扮演重要的角色,所以我們 針對不同的 Ge 摻雜濃度的莫耳分率做分析。模擬結果顯示 Ge 的濃度愈高,直流電流增益愈顯著。

元件在工作中會產生自我加熱效應(self-heating effect) 的問題在所有的 SOI 技術中是一個眾所皆知的缺點。我們探討了絕緣層上覆矽之矽鍺異質結構雙極性電晶體元件本身自我加熱效應隨著不同的集極厚度  $T_{\rm C}$ 之厚度的變化,分析結果顯示熱電阻隨著集極厚度  $T_{\rm C}$ 的增加而下降。如同前文所述,氧化層的加入勢必造成阻礙散熱的相當影響、增加

熱電阻。這樣的模擬結果,讓我們在使用 SOI 結構時可以配合集極厚度的適當選擇,來改善熱效應。

圖 3-1 元件的能帶圖。電晶體的偏壓條件是  $V_B = 0.6V$  and  $V_C = 1V$  。

圖 3-2 SOI SiGe npn HBT。

圖 3-3 SOI 與 Bulk 結構之 SiGe HBT 輸出特性

圖 3-4 SOI 結構之 SiGe HBT 在 5%的 Ge 摻雜濃度的莫耳 分率的情況下  $I_C$ 和  $I_B$ 對  $V_{BE}$ 的特性曲線圖。

圖 3-5. SOI 結構之 SiGe HBT 在 10 %的 Ge 摻雜濃度的莫耳分率的情况下  $I_{\rm C}$ 和  $I_{\rm B}$ 對  $V_{\rm BE}$  的特性曲線圖。

圖 3-6 SOI 結構之 SiGe HBT 在 10 %的 Ge 摻雜濃度的莫耳 分率的情況下  $I_C$  和  $I_B$  對  $V_{BE}$  的特性曲線圖。

圖 3-7 SOI 結構之 SiGe HBT 在 10 %的 Ge 摻雜濃度的莫耳 分率的情況下  $I_C$  和  $I_B$  對  $V_{BE}$  的特性曲線圖。

圖 3-9 熱阻與集極厚度的關係。

# 參考文獻:

- Patton, G. L., S. S. Iyer, S.L. Delage, S.J.M.C.Stork (1988) Silicon-germanium base heterojunction bipolar transistors by molecular beam epitaxy, *IEEE Electron Device Letters* 9, 165.

- Tron, B. L., M. D. R. Hashim, P. Ashburm, M. Mouis, A. Chanter, and G. Vincent (1997) Determination of bandgap narrowing and parasitic energy barrier in SiGe HBT's Integrated in a bipolar technology, *IEEE Trans. Electron Devices*, 44, 715.

- Rieh, J. S., K. M. Watson, F. Guarin, Z. Yang, P. C. Wang, A. J. Joseph, G. Freeman, and S. Subbanna (2003) Reliability of high-speed SiGe Heterojunction bipolar transistors under very highforward current density, *IEEE Trans. Electron Devices*, 3, 31.

- Chang, S. T., C. W. Liu, and S. C. Lu (2004) Base transit time of graded-base Si/SiGe HBTs considering recombination lifetime and velocity saturation, *Solid-State Electronics* 48,207.

- Khanduri, G., B. Panwar, (2006) A study of the effects of the base doping profile on SiGe heterojunction bipolar transistor performance for all levels of Injection, *Semicond. Sci. Technol.* 21, 486.

- Harame, D. L., J. H. Comfort, J. D. Cressler, E. F. Crabbe, J. Y. C. Sun, B. S. Meyerson and T. Tice (1995) Si/SiGe Epitaxial-Base Transistors-Part I: Materials, Physics and Circuits, *IEEE Trans. Electron Devices* 42, 455.

- Kroemer, H. (1985) Two Integral Relations Pertaining to The Electron Transport Through a Bipolar Transistor With a Non Uniform Energy Gap in The Base Region, Solid-State Electron., 28, 1101.

- Singer, R., D. L. Harame, and M. M. Oprysko (2004)

Silicon Germanium Technology, Modeling, and Design, 89,

New York, John Wiley. & Sons inc.

- Bovolon, N., P. Baureis, J.-E. Muller, P. Zwicknagl, R. Schultheis, and E. Zanoni (1998) A Simple Method for The Thermal Resistance Measurement of AlGaAs/GaAs Heterojunction Bipolar Transistors, *IEEE Trans. Electron Devices*, 45, 1846.

- Palestri, P., A. Pacelli, M. Mastrapasqua (2001) Thermal resistance in Si<sub>1-x</sub>Ge<sub>x</sub> HBTs on bulk-Si and SOI substrates, in Proc. BCTM, 98.

- Rieh, J. –S., D. Greenberg, B. Jagannathan, G. Freeman, S. Subbanna (2001) Measurement and Modeling of Thermal Resistance of High Speed SiGe Heterojunction Bipolar Transistors, in Proc. Topical Meeting Silicon Monolithic Integrated Circuits in RF Systems, 110.

- Vanhoucke, T., H. M. J. Boots, and W. D. Van Noot (2004)

Revised Method for Extraction of the Thermal Resistance

Applied to Bulk and SOI SiGe HBTs, *IEEE Electron Device Lett.* 25, 150.

- 13. 劉博文 (民 92), 半導體元件物理, 高立圖書有限公司